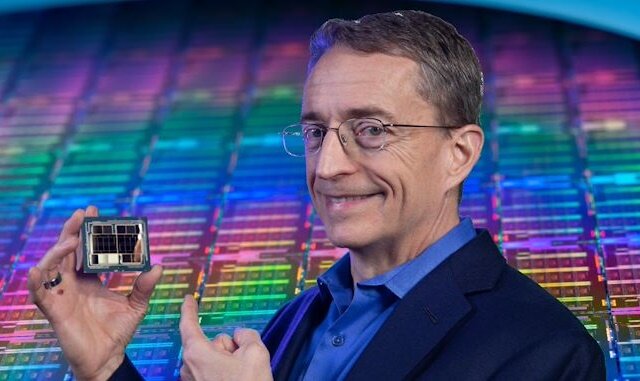

인텔의 CEO인 팻 겔싱어(Pat Gelsinger)는 오늘(25일) JP Morgan Global TMC Week 행사에서 7나노 메테오레이크의 컴퓨팅 타일을 테이프 인(taped-in) 한다고 발표했다. 테이프 인은 넌 모놀리식(non-monolithic - 비 일체형)설계에 사용되는 새로운 용어로 설계에 사용할 수 있는 수준으로 검증되었다는 뜻이다.

발표에서는 추가 SoC(단일 칩 시스템) 검증 후 최종 결과물을 공장에 내보낼 준비가 되어있으며, 생산을 위해 파운드리로 보낼 예정이라고 언급했다.

이에 팻 겔싱어는 "우리는 과거의 10nm 칩부터 현재 7nm 칩까지 제작하는데 있어 많은 어려움을 극복했다. 그리고 웨이퍼에 대한 업데이트 문제는 반도체 공정 중 하나인 EUV 공정(극자외선 파장의 광원을 활용한 제조공정)의 전면적인 수용으로 다시 정상 궤도에 올려놓을 것이라고 확신한다"라고 말했다.

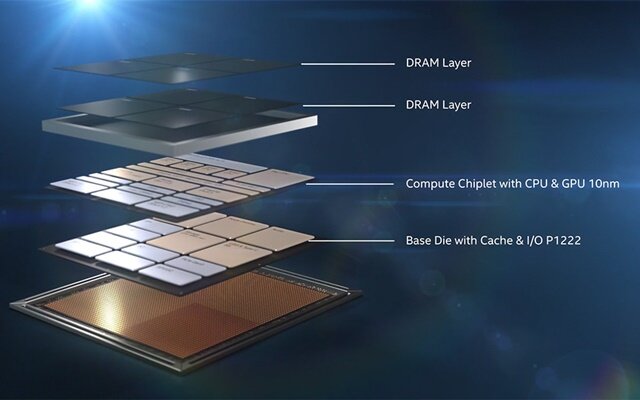

7나노 메테오레이크는 인텔의 7nm 프로세스를 기반으로 하며 포베로스(Foveros) 기술이 들어가 있는 것으로 알려졌다. 포베로스 기술은 다양한 메모리 및 I/O 요소를 갖춘 IP 블록을 작은 크기의 패키지에 담을 수 있으며, 이에 따라 보드 크기도 현저히 줄일 수 있는 장점이 있다. 이 기술은 인텔의 레이크필드 칩에서도 볼 수 있듯이 다이 온 다이(die-on-die) 로직 스태킹을 통해 3D 프로세서를 제작할 수 있다.